CPU: Pipeline 은 무엇인가?

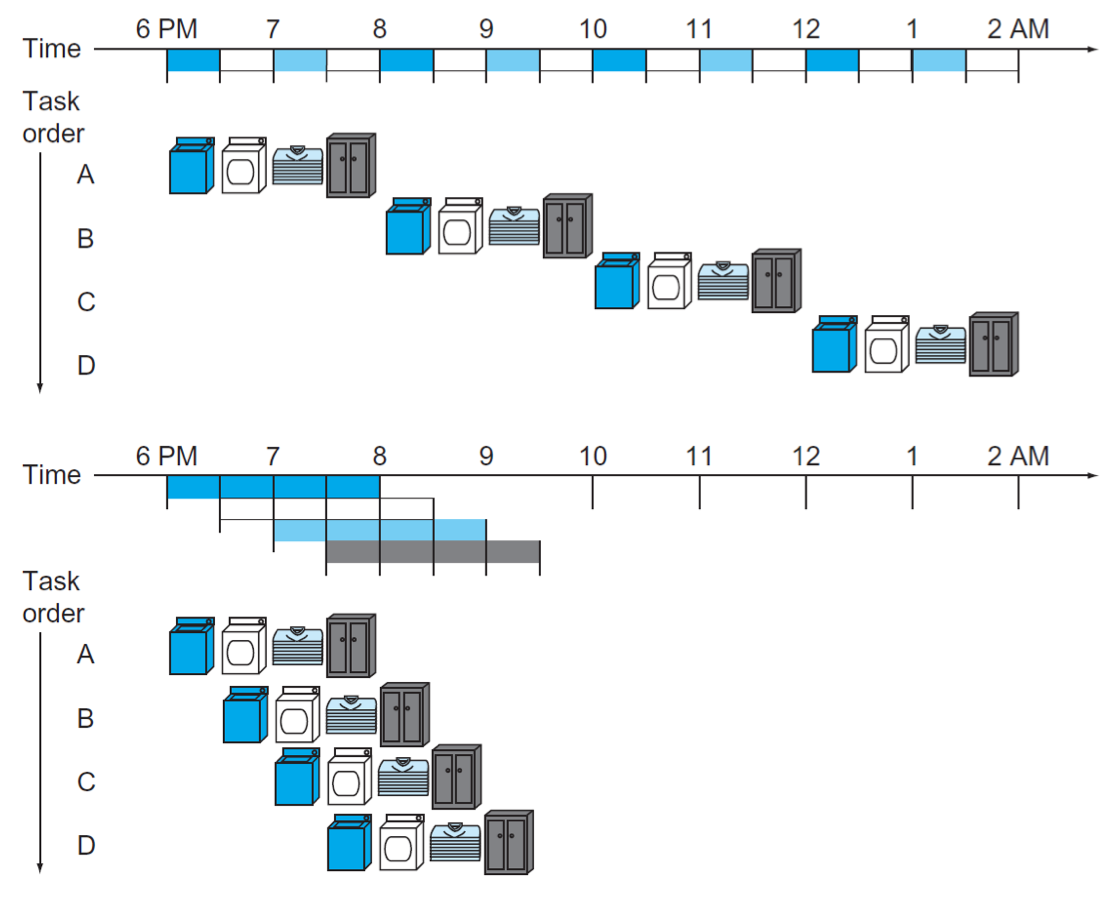

파이프라인의 동작 원리: 조립 라인 비유

파이프라인의 동작은 자동차 공장의 조립 라인에 비유하면 가장 이해하기 쉽습니다.

단일 작업자 방식 (단일 사이클 프로세서): 작업자 한 명이 자동차 한 대를 처음부터 끝까지 (부품 조립, 도색, 검사 등 모든 공정) 혼자서 다 완성합니다. 한 대가 완전히 끝나야 다음 대를 시작할 수 있습니다.

단점: 작업자가 다음 공정을 기다리는 동안 이전 공정 장비는 놀게 됩니다. 전체 생산 속도가 가장 느린 공정에 의해 제한됩니다.

조립 라인 방식 (파이프라인 프로세서): 여러 작업자가 각각 다른 공정을 전담합니다.

1번 작업자: 부품 조립 (1단계)

2번 작업자: 도색 (2단계)

3번 작업자: 검사 (3단계)

자동차 한 대가 1번 작업자에게서 완성되면, 1번 작업자는 다음 자동차를 시작하고, 첫 번째 자동차는 2번 작업자에게로 넘어갑니다. 동시에 1번 작업자는 두 번째 자동차를 작업하고, 2번 작업자는 첫 번째 자동차를 작업합니다.

결과: 처음 자동차가 완성되는 데는 이전과 동일한 시간이 걸리지만, 일단 라인이 가동되면 매 순간 새로운 자동차가 한 대씩 완성됩니다. 전체적인 생산량이 폭발적으로 늘어납니다.

MIPS 5단계 파이프라인의 시간별 동작 시퀀스

MIPS의 5단계 파이프라인 (IF, ID, EX, MEM, WB)에 이 조립 라인 비유를 적용하여, 여러 명령어(I1, I2, I3, I4, I5...)가 어떻게 동시에 실행되는지 클럭 사이클(Cycle)별로 살펴보겠습니다. 각 클럭 사이클은 가장 긴 단계의 시간(예: 200 ps)과 동일합니다.

| 클럭 사이클 (Cycle) | Stage 1 (IF) | Stage 2 (ID) | Stage 3 (EX) | Stage 4 (MEM) | Stage 5 (WB) |

|---|---|---|---|---|---|

| 1 | I1 (명령어 인출) | ||||

| 2 | I2 (명령어 인출) | I1 (해독/레지스터) | |||

| 3 | I3 (명령어 인출) | I2 (해독/레지스터) | I1 (실행) | ||

| 4 | I4 (명령어 인출) | I3 (해독/레지스터) | I2 (실행) | I1 (메모리 접근) | |

| 5 | I5 (명령어 인출) | I4 (해독/레지스터) | I3 (실행) | I2 (메모리 접근) | I1 (레지스터 쓰기) |

| 6 | ... | I5 (해독/레지스터) | I4 (실행) | I3 (메모리 접근) | I2 (레지스터 쓰기) |

| 7 | ... | ... | I5 (실행) | I4 (메모리 접근) | I3 (레지스터 쓰기) |

설명:

클럭 사이클 1: 첫 번째 명령어

I1이 IF 단계에 진입하여 명령어 메모리에서 인출됩니다.클럭 사이클 2:

I1은 다음 파이프라인 레지스터(IF/ID)를 통과하여 ID 단계에 진입하고 해독됩니다. 동시에, 두 번째 명령어I2가 IF 단계에 진입하여 인출됩니다.클럭 사이클 3:

I1은 EX 단계에서 실행되고,I2는 ID 단계에서 해독되며,I3은 IF 단계에서 인출됩니다.클럭 사이클 4:

I1은 MEM 단계로,I2는 EX 단계로,I3은 ID 단계로,I4는 IF 단계로 각각 한 칸씩 이동합니다.클럭 사이클 5:

I1은 마침내 WB 단계에서 완료되어 결과를 레지스터에 씁니다. 동시에I2는MEM,I3은EX,I4는ID,I5는IF단계를 수행합니다.이 시점부터는 이상적인 경우, 매 클럭 사이클마다 하나의 명령어가 완료됩니다. (

I1이 완료된 클럭 사이클 5에서I2는MEM단계이므로, 다음 클럭 사이클 6에서I2가 완료됩니다.)

파이프라인의 핵심 요소와 원리

동시성 (Concurrency): 여러 명령어가 파이프라인의 서로 다른 단계에서 동시에 실행됩니다. 각 단계는 해당 명령의 특정 부분만 처리합니다.

분할 (Partitioning): 명령어 실행을 여러 개의 독립적인 작은 단계로 나눕니다. 각 단계는 특정 하드웨어 자원을 사용합니다.

병렬 실행 (Parallel Execution): 각 단계는 서로 다른 명령어를 동시에 처리하므로, 전체 명령어 처리율(Throughput)이 향상됩니다.

파이프라인 레지스터 (Pipeline Registers / Latches): 각 단계 사이에 위치하여, 이전 단계의 출력값을 저장하고 다음 단계로 전달합니다. 이는 단계 간의 동기화와 독립적인 작동을 가능하게 합니다. 각 클럭 사이클의 끝에서 이 레지스터들의 내용이 업데이트됩니다.

클럭 주기 단축: 전체 명령어가 하나의 긴 클럭 주기 안에 실행되는 단일 사이클 프로세서와 달리, 파이프라인 프로세서의 클럭 주기는 가장 긴 단일 단계의 시간으로 결정됩니다. 이는 프로세서가 더 높은 클럭 주파수에서 작동할 수 있게 하여 전체적인 성능을 높입니다.

장점:

높은 처리율 (High Throughput): 단위 시간당 더 많은 명령어를 완료할 수 있습니다.

클럭 주파수 증가: 각 단계가 더 짧은 시간 안에 완료되므로 더 빠른 클럭 속도로 동작할 수 있습니다.

단점:

해저드 (Hazard) 발생 가능성: 명령어 간의 종속성이나 자원 충돌로 인해 파이프라인의 흐름이 방해받을 수 있습니다. (데이터 해저드, 제어 해저드, 구조 해저드)

하드웨어 복잡성 증가: 파이프라인 레지스터, 해저드 감지/해결 로직(포워딩, 스톨), 제어 유닛의 복잡성 등이 추가됩니다.

첫 명령어의 긴 지연 시간 (Latency): 첫 번째 명령어가 완료되는 데 걸리는 시간(파이프라인 깊이 * 클럭 사이클 시간)은 단일 사이클 프로세서와 동일하거나 더 길 수 있습니다. (그러나 전체적인 처리율이 중요)