CPU: 파이프라인 명령어 type별 동작 원리

MIPS 메모리 표현 방식(Addressing Mode)에 따른 파이프라인 동작 과정

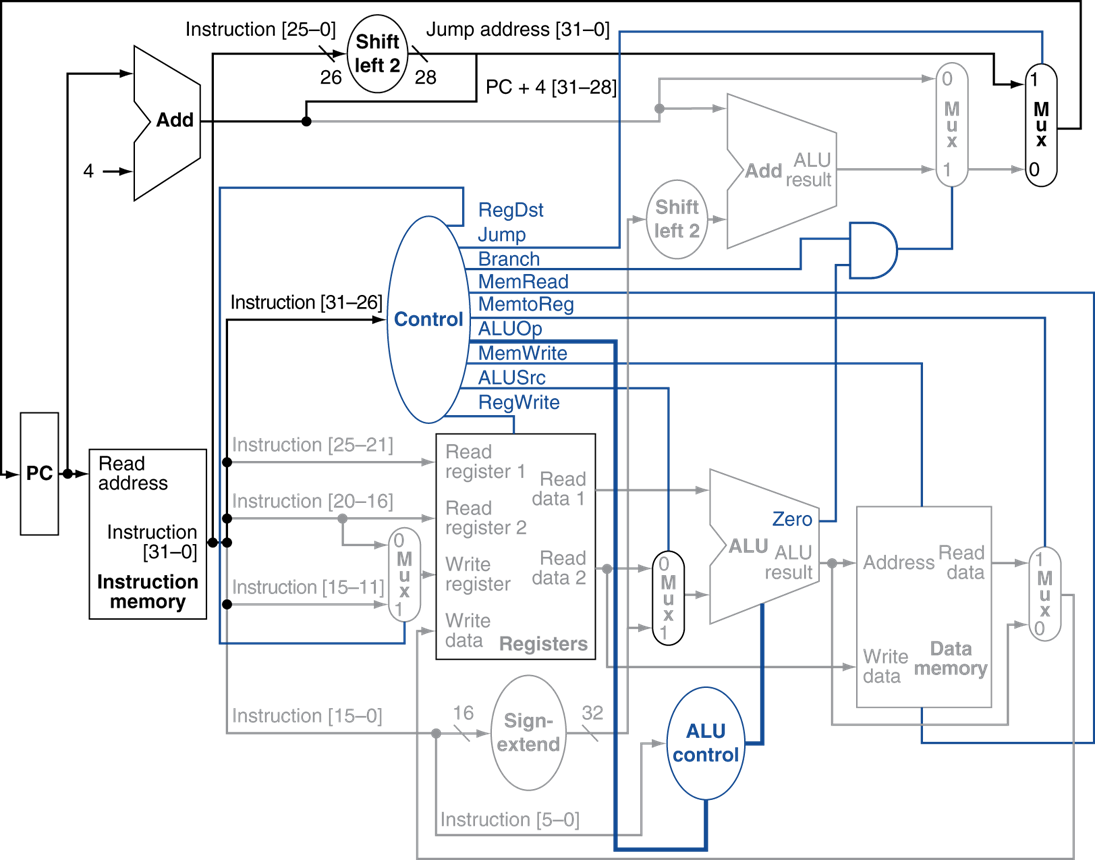

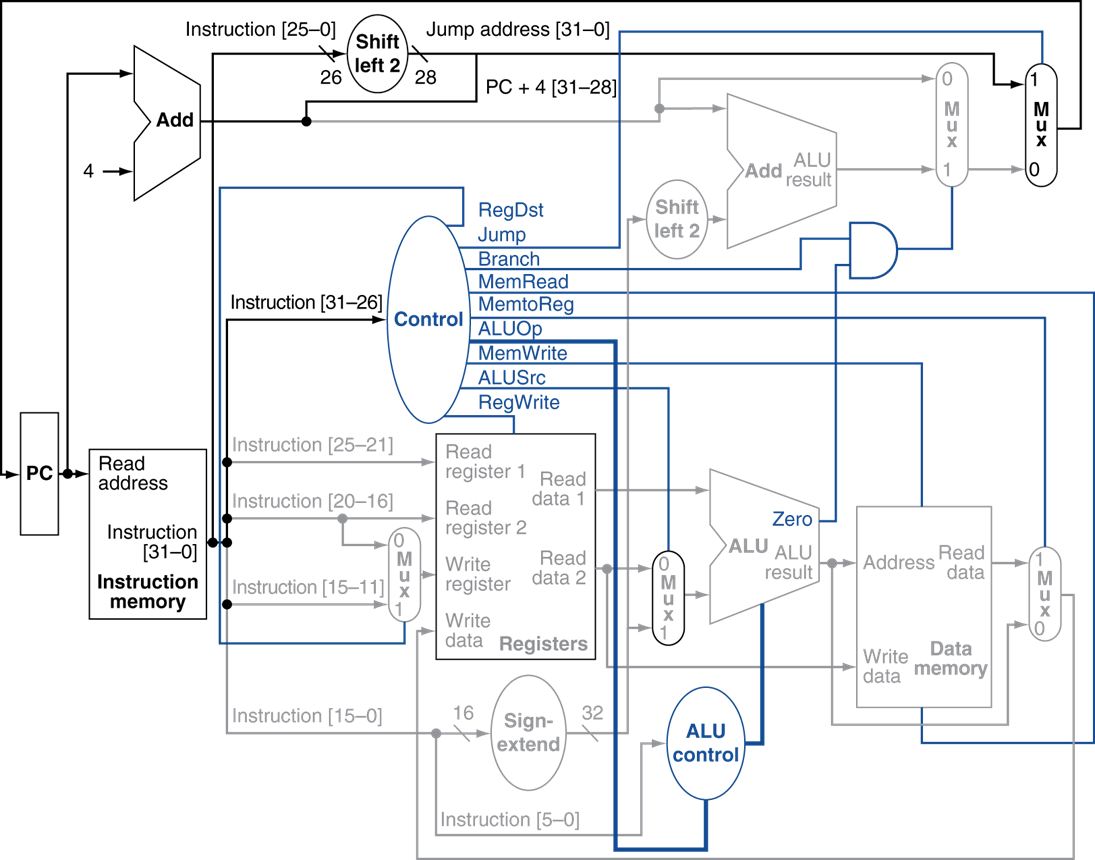

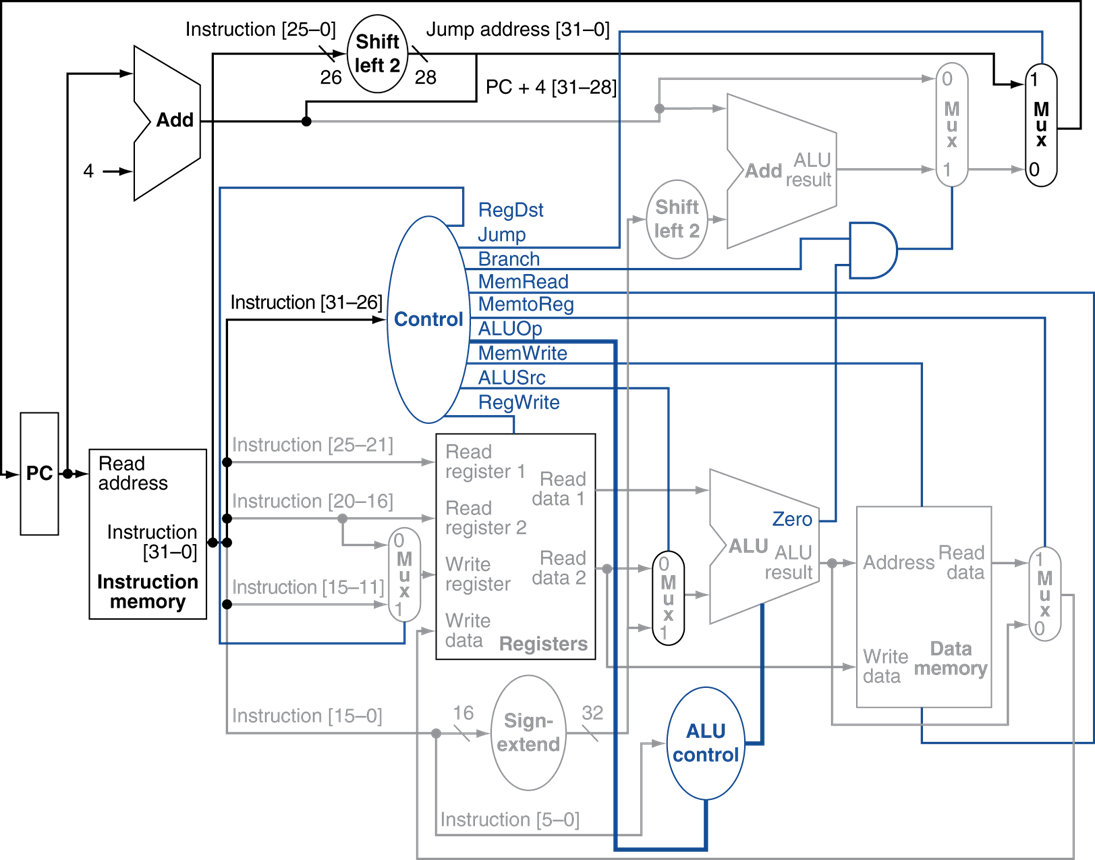

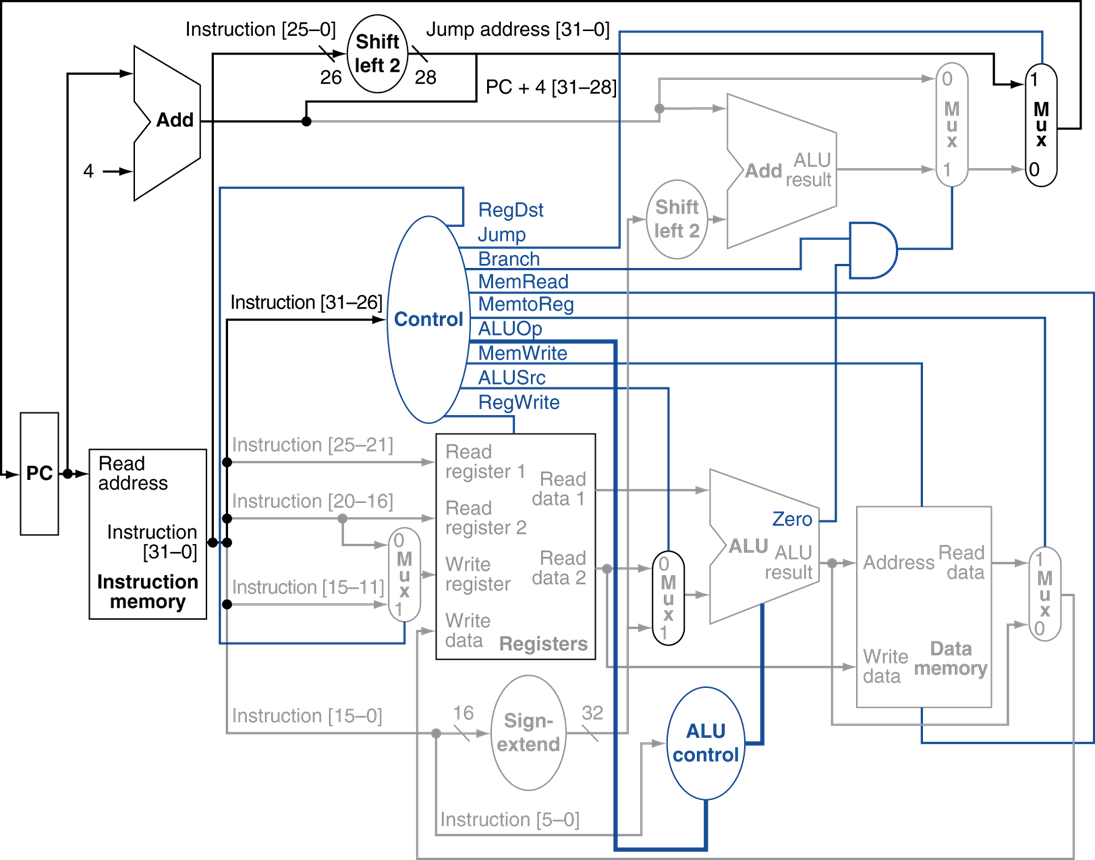

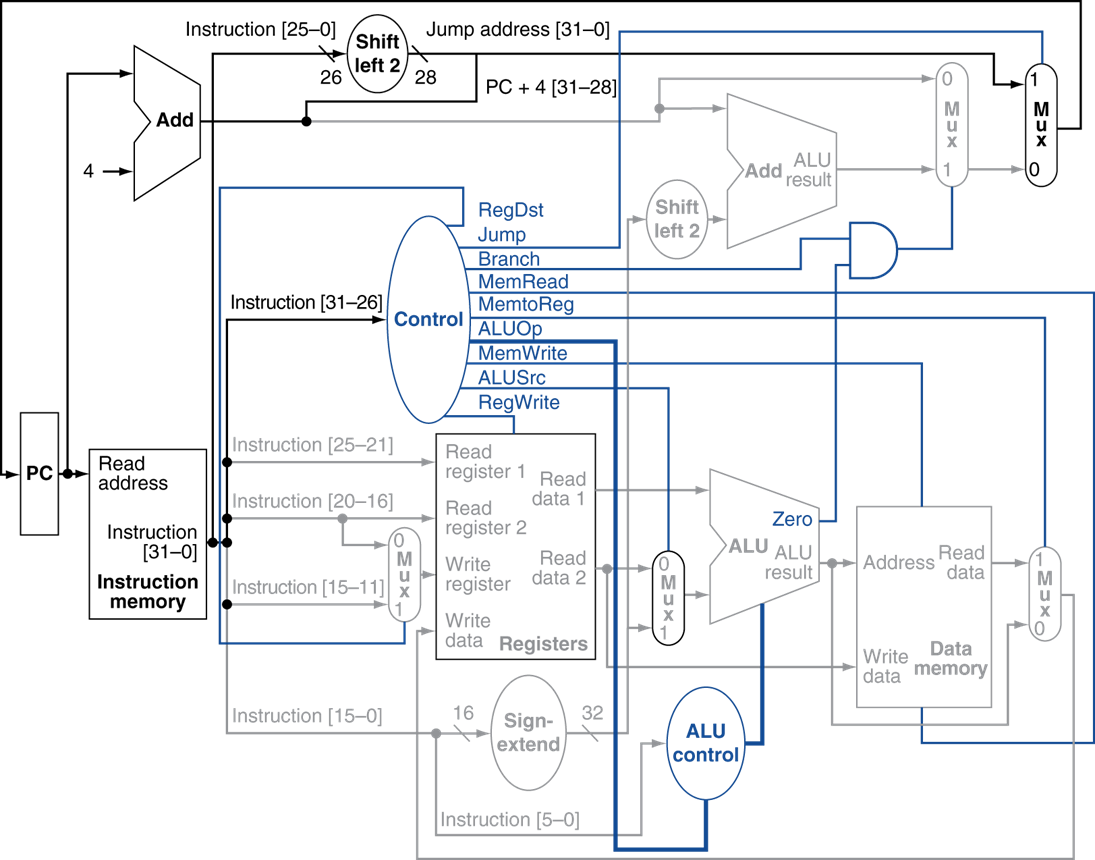

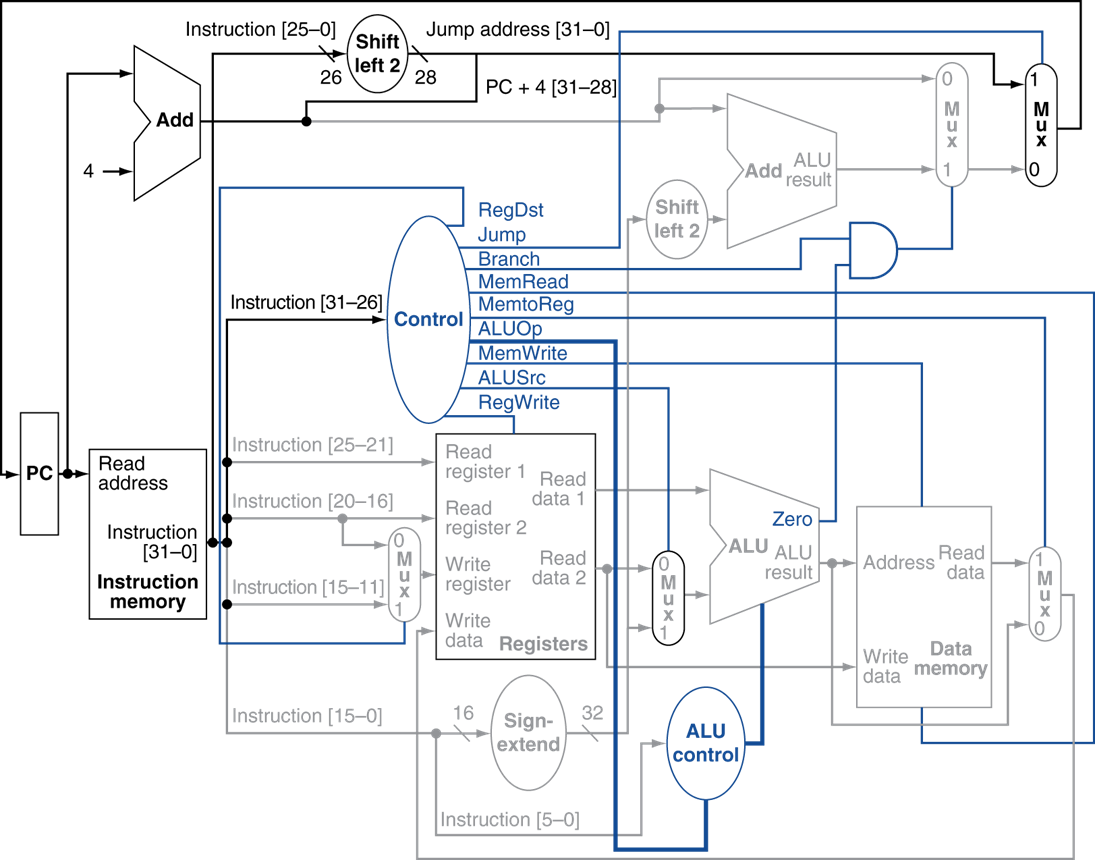

MIPS의 명령어 형식과 주소 지정 기법은 파이프라인의 각 단계에 명확하고 예측 가능한 영향을 미치도록 설계되었습니다. 각 주소 지정 모드가 파이프라인의 어느 단계에서 활성화되고 어떤 작업을 유발하는지 자세히 살펴보겠습니다.

1. 레지스터 주소 지정 (Register Addressing) - R-Type 명령어

관련 명령어 예시:

add $t0, $s1, $s2,sub $t0, $s1, $s2,and $t0, $s1, $s2,jr $ra등특징: 피연산자가 모두 레지스터에 있습니다. 메모리 접근이 일체 없습니다.

파이프라인 동작 과정:

IF (Instruction Fetch):

PC가 가리키는 주소에서 32비트 R-Type 명령어를 명령어 메모리(IM)에서 인출하여

IF/ID레지스터에 저장합니다.PC는

PC + 4로 업데이트됩니다.

ID (Instruction Decode / Register Fetch):

IF/ID레지스터의 R-Type 명령어를 해독합니다.op필드(000000)와funct필드를 통해 명령의 종류(add,sub등)를 식별합니다. --> Control Unit 으로 이동rs및rt필드(5비트)를 사용(각각 Read register 1, Read register 2로 이동)하여Register File에서 해당 레지스터 값들을 읽어와ID/EX레지스터로 전달합니다. (두 개의 Read Port 활용)rd필드(5비트)를 write register에 전달해 저장되기 위한 레지스터의 주소값을 지정합니다.(MIPS는 총 32개의 register를 가지고 있어, 5비트로 레지스터 주소값을 표현 가능)Control Unit은 R-Type 연산에 필요한 제어 신호들을 생성하여ID/EX레지스터로 보냅니다.

EX (Execute):

ID/EX레지스터에서 읽어온 두 레지스터 값(rs,rt)을 ALU의 입력으로 사용합니다.ALU Control신호에 따라 ALU는add,sub,and등 해당 R-Type 연산을 수행합니다.ALU 결과와 쓰기 레지스터 주소(

rd또는rt필드),RegWrite제어 신호 등을EX/MEM레지스터로 전달합니다. (메모리 접근 없음)

MEM (Memory Access):

데이터 메모리에 접근하지 않습니다.

EX/MEM레지스터의 내용(ALU 결과, 쓰기 레지스터 주소 등)을 그대로MEM/WB레지스터로 전달합니다. (MemRead/MemWrite 제어 신호는 비활성화됨)

WB (Write Back):

MEM/WB레지스터에 있는 ALU 결과 값을Register File의rd레지스터(또는rt레지스터, 명령어에 따라 다름)에 씁니다. (RegWrite신호 활성화)jr(Jump Register) 명령어의 경우, ALU 결과가 레지스터에 쓰이는 것이 아니라,rs레지스터의 값이 PC로 업데이트되어 제어 흐름이 변경됩니다. 이 업데이트는 EX 단계 후 ID 단계의 PC 업데이트 로직에 영향을 줍니다.

2. 즉시 주소 지정 (Immediate Addressing) - I-Type 명령어 중 상수 연산

관련 명령어 예시:

addi $t0, $s1, 100,andi $t0, $s1, 0xFF,slti $t0, $s1, 5등특징: 피연산자 중 하나가 명령어 자체 내에 포함된 상수(즉시값)입니다. 메모리 접근이 일체 없습니다.

파이프라인 동작 과정:

IF (Instruction Fetch):

PC가 가리키는 주소에서 32비트 I-Type 명령어를 인출하여

IF/ID레지스터에 저장합니다.PC는

PC + 4로 업데이트됩니다.

ID (Instruction Decode / Register Fetch):

IF/ID레지스터의 I-Type 명령어를 해독합니다.op필드를 통해addi,andi등의 명령 종류를 식별합니다.rs필드를 사용하여Register File에서 해당 레지스터 값을 읽어와ID/EX레지스터로 전달합니다.16비트

immediate필드를Sign Extender(또는Zero Extenderforandi,ori,xori)를 통해 32비트로 확장하여ID/EX레지스터로 전달합니다.Control Unit은 I-Type 연산에 필요한 제어 신호들을 생성하여ID/EX레지스터로 보냅니다.

EX (Execute):

ID/EX레지스터에서 읽어온rs레지스터 값과 확장된 16비트 즉시값을 ALU의 입력으로 사용합니다. (ALU Source Mux가 즉시값 선택)ALU Control신호에 따라 ALU는addi,andi등 해당 연산을 수행합니다.ALU 결과와 쓰기 레지스터 주소(

rt필드),RegWrite제어 신호 등을EX/MEM레지스터로 전달합니다.

MEM (Memory Access):

데이터 메모리에 접근하지 않습니다.

EX/MEM레지스터의 내용을 그대로MEM/WB레지스터로 전달합니다.

WB (Write Back):

MEM/WB레지스터에 있는 ALU 결과 값을Register File의rt레지스터에 씁니다. (RegWrite신호 활성화)

값을 계산하는 R-format 명령어(예: add, sub, and)와 I-format의 immediate 연산 명령어(예: addi, andi, slti)의 경우, 메모리에 관련된 모든 컨트롤 유닛 신호는 꺼져 있습니다.

이 명령어들은 데이터를 메모리에서 읽거나(load) 쓰지(store) 않고, 오직 CPU 내부의 레지스터들 간 또는 레지스터와 즉시값 간의 연산만 수행하기 때문입니다. --> MemtoReg 값 또한 0으로 꺼져 있어야 ALU 연산만 진행한 값이 write data에 전달되어 write register(rt필드 레지스터)에 저장됩니다.

구체적으로 꺼져 있는 메모리 관련 제어 신호들은 다음과 같습니다:

MemRead(Memory Read): 0 (데이터 메모리에서 읽기 비활성화)MemWrite(Memory Write): 0 (데이터 메모리에 쓰기 비활성화)MemToReg(Memory to Register): 0 (레지스터에 쓸 데이터 소스를 ALU 결과로 선택)

3. 기본/변위 주소 지정 (Base/Displacement Addressing) - I-Type 명령어 중 메모리 접근

관련 명령어 예시:

lw $t0, 100($s1),sw $t0, 100($s1),lb $t0, 0($s1)등특징: 메모리에 저장된 데이터에 접근하며, 주소는 베이스 레지스터 값과 명령어 내 오프셋의 합으로 계산됩니다.

파이프라인 동작 과정:

IF (Instruction Fetch):

PC가 가리키는 주소에서 32비트 Load/Store 명령어를 인출하여

IF/ID레지스터에 저장합니다.PC는

PC + 4로 업데이트됩니다.

ID (Instruction Decode / Register Fetch):

IF/ID레지스터의 Load/Store 명령어를 해독합니다.op필드를 통해lw,sw등의 명령 종류를 식별합니다.rs필드(베이스 레지스터)를 사용하여Register File에서 해당 레지스터 값을 읽어와ID/EX레지스터로 전달합니다.16비트

offset필드를Sign Extender를 통해 32비트로 부호 확장하여ID/EX레지스터로 전달합니다.Control Unit은 메모리 접근에 필요한 제어 신호들(MemRead,MemWrite,MemToReg,RegWrite등)을 생성하여ID/EX레지스터로 보냅니다.

EX (Execute):

ID/EX레지스터에서 읽어온rs레지스터 값과 확장된offset값을 ALU의 입력으로 사용합니다. (ALU Source Mux가 즉시값 선택)ALU는 이 두 값을 더하여 데이터 메모리의 유효 주소(Effective Address)를 계산합니다.

sw명령의 경우,rt레지스터의 값(메모리에 저장할 데이터)도EX/MEM레지스터로 전달됩니다.계산된 주소,

rt레지스터 값, 제어 신호(MemRead,MemWrite,MemToReg,RegWrite등)를EX/MEM레지스터로 전달합니다.

MEM (Memory Access):

EX/MEM레지스터에서 계산된 메모리 주소와 제어 신호(MemRead,MemWrite)를 가져옵니다.데이터 메모리(DM)에 실제로 접근합니다.

lw,lb,lh등 Load 명령인 경우:MemRead가 활성화되어 해당 주소에서 데이터를 읽어옵니다. 읽어온 데이터는MEM/WB레지스터로 전달됩니다.sw,sb,sh등 Store 명령인 경우:MemWrite가 활성화되어EX/MEM레지스터에 있던rt레지스터의 값을 해당 주소에 씁니다. (Store 명령은 WB 단계에서 레지스터에 쓰지 않으므로RegWrite가 비활성화됨)

정렬 검사: 이 단계에서 주소의 정렬 상태가 검사되며, 조건이 충족되지 않으면 예외가 발생할 수 있습니다.

WB (Write Back):

Load 명령인 경우만 레지스터에 씁니다.

MEM/WB레지스터에 있는 메모리에서 읽어온 데이터를Register File의rt레지스터에 씁니다. (MemToRegMux가 메모리 데이터 선택,RegWrite활성화)Store 명령은 WB 단계에서 아무것도 하지 않습니다.

4. PC-상대 주소 지정 (PC-Relative Addressing) - I-Type 명령어 중 조건부 분기

관련 명령어 예시:

beq $t0, $t1, Label,bne $t0, $t1, Label특징: 점프할 목적지 주소가 현재 PC 값과 명령어 내 오프셋의 합으로 계산됩니다.

파이프라인 동작 과정:

IF (Instruction Fetch):

PC가 가리키는 주소에서 32비트 분기 명령어를 인출하여

IF/ID레지스터에 저장합니다.PC는

PC + 4로 미리 업데이트됩니다. (분기 발생 여부를 아직 모르기 때문에)

ID (Instruction Decode / Register Fetch):

IF/ID레지스터의 분기 명령어를 해독합니다.op필드를 통해beq,bne명령 종류를 식별합니다.rs및rt필드를 사용하여Register File에서 해당 레지스터 값들을 읽어와ID/EX레지스터로 전달합니다. (비교 연산에 사용)16비트

offset필드를Sign Extender를 통해 32비트로 부호 확장한 후,Shift Left 2(워드 오프셋을 바이트 오프셋으로 변환)를 수행하여ID/EX레지스터로 전달합니다.이 단계에서 잠재적인 분기 목적지 주소

(PC_from_IF/ID + 4) + (SignExt(offset) << 2)를 계산해 둡니다.Control Unit은 분기에 필요한 제어 신호(Branch등)를 생성합니다.

EX (Execute):

ID/EX레지스터에서 읽어온rs및rt레지스터 값을 ALU의 입력으로 사용합니다.ALU는 이 두 값을 비교하여 분기 조건(

rs == rt또는rs != rt)을 평가합니다. (예:rs - rt연산 후 결과가 0인지 검사, ALU의 Zero는 비교 연산 확인을 위해 사용됩니다.)분기 조건이 참인 경우:

PC_Source Mux가 ID 단계에서 계산해 둔 분기 목적지 주소를 선택하도록 제어 신호(Branch와 ALU의 Zero flag 조합)가 발생합니다. 다음 클럭 사이클 시작 시 이 주소로 PC가 업데이트됩니다. (이때, IF/ID, ID/EX 래치에 있는 파이프라인의 명령어가 잘못 인출된 것이므로 플러시(Flush) 됩니다 - 제어 해저드 처리, 추후 다룸.).분기 조건이 거짓인 경우: PC는

PC + 4경로를 그대로 유지합니다.

MEM (Memory Access):

데이터 메모리 접근 없음. 이 단계에 도달한 분기 명령은 이미 EX 단계에서 PC 업데이트 여부를 결정했습니다.

WB (Write Back):

레지스터 쓰기 없음. 분기 명령어는 레지스터에 값을 쓰지 않습니다.

5. 가상 직접 주소 지정 (Pseudodirect Addressing) - J-Type 명령어

관련 명령어 예시:

j Label,jal Label특징: 절대 주소로 무조건 점프하며, 주소는 명령어 내 26비트 주소 필드와 현재 PC의 상위 비트를 조합하여 생성됩니다.

파이프라인 동작 과정:

IF (Instruction Fetch):

PC가 가리키는 주소에서 32비트 J-Type 명령어를 인출하여

IF/ID레지스터에 저장합니다.PC는

PC + 4로 미리 업데이트됩니다.

ID (Instruction Decode / Register Fetch):

IF/ID레지스터의 J-Type 명령어를 해독합니다.op필드를 통해j,jal명령 종류를 식별합니다.명령어의 26비트

target address필드를 가져옵니다.Control Unit은 점프에 필요한 제어 신호(Jump등)를 생성합니다.

EX (Execute):

ID 단계에서 가져온 26비트

target address를Shift Left 2(워드 주소를 바이트 주소로 변환) 한 후, 현재 PC의 상위 4비트와 결합하여 최종 32비트 절대 점프 주소를 생성합니다.이 절대 점프 주소는

PC_Source Mux가 선택하도록 제어 신호(Jump)가 발생합니다. 다음 클럭 사이클 시작 시 이 주소로 PC가 업데이트됩니다. (이때도Branch와 유사하게 파이프라인 플러시 발생 - 제어 해저드 처리).jal명령의 경우,PC + 4(즉, 복귀 주소)를$ra레지스터에 저장할 준비를 합니다. (이 저장은 WB 단계에서 이루어집니다.)

MEM (Memory Access):

데이터 메모리 접근 없음.

WB (Write Back):

jal명령인 경우:EX단계에서 준비된PC + 4값을Register File의$ra레지스터에 씁니다.j명령은 WB 단계에서 아무것도 하지 않습니다.

6. 점프 레지스터 주소 지정 (Jump Register Addressing) - R-Type 명령어 중 제어 흐름 변경

관련 명령어 예시:

jr $ra,jalr $s0특징: 점프할 목적지 주소가 레지스터에 저장되어 있습니다.

파이프라인 동작 과정:

IF (Instruction Fetch):

PC가 가리키는 주소에서 32비트

jr명령어를 인출하여IF/ID레지스터에 저장합니다.PC는

PC + 4로 미리 업데이트됩니다.

ID (Instruction Decode / Register Fetch):

IF/ID레지스터의jr명령어를 해독합니다.op필드(000000)와funct필드(jr의 funct 코드)를 통해 명령 종류를 식별합니다.rs필드(점프할 주소가 담긴 레지스터)를 사용하여Register File에서 해당 레지스터 값을 읽어와ID/EX레지스터로 전달합니다.Control Unit은jr에 필요한 제어 신호를 생성합니다.

EX (Execute):

ID/EX레지스터에서 읽어온rs레지스터 값(점프할 목적지 주소)을 가져옵니다.이

rs값은PC_Source Mux가 선택하도록 제어 신호가 발생합니다. 다음 클럭 사이클 시작 시 이 주소로 PC가 업데이트됩니다. (jr도 제어 해저드 처리 필요)jalr명령의 경우,PC + 4(복귀 주소)를$rd레지스터에 저장할 준비를 합니다.

MEM (Memory Access):

데이터 메모리 접근 없음.

WB (Write Back):

jalr명령인 경우:EX단계에서 준비된PC + 4값을Register File의$rd레지스터에 씁니다.jr명령은 WB 단계에서 아무것도 하지 않습니다.