CPU: Pipeline Register란?

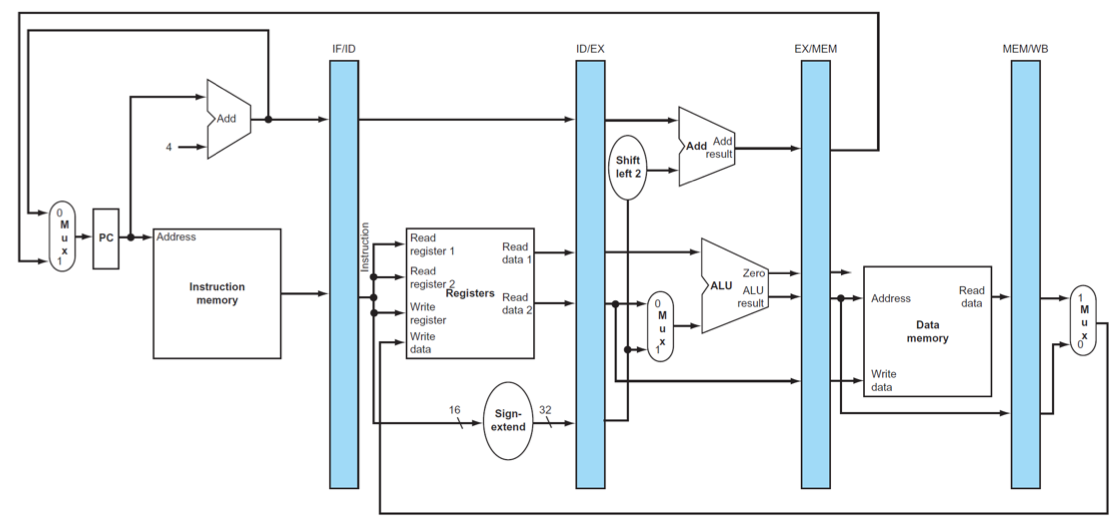

파이프라인 레지스터(Pipeline Register)는 컴퓨터 아키텍처에서 명령어 파이프라인의 각 단계(stage) 사이에 위치하여, 이전 단계의 결과를 저장하고 다음 단계로 전달하는 역할을 하는 특별한 레지스터입니다. 이를 통해 여러 명령어가 동시에 파이프라인의 다른 단계에 걸쳐 실행될 수 있도록 하여 CPU의 처리량(throughput)을 크게 향상시킵니다.

쉽게 비유하자면, 세탁, 건조, 다림질의 세 단계로 이루어진 세탁 과정을 생각해보세요. 파이프라인이 없다면 한 세탁물이 세 단계를 모두 마친 후에야 다음 세탁물이 세탁을 시작할 수 있습니다. 하지만 파이프라인이 있다면, 첫 번째 세탁물이 건조 중일 때 두 번째 세탁물은 세탁을 시작할 수 있고, 세 번째 세탁물은 다림질을 할 수 있습니다. 이 경우 각 세탁물 사이에는 바구니(파이프라인 레지스터)가 있어서 한 단계가 끝난 옷을 다음 단계로 넘겨주는 역할을 합니다.

CPU 파이프라인의 일반적인 5단계(MIPS 아키텍처 기준)와 각 파이프라인 레지스터에 저장되는 값은 다음과 같습니다.

각 파이프라인 레지스터에 저장되는 값

각 단계의 출력이 다음 단계의 입력으로 사용될 때, 이 값들이 파이프라인 레지스터에 저장됩니다. 파이프라인 레지스터의 이름은 일반적으로 연결하는 두 단계의 이름을 따서 명명됩니다 (예: IF/ID).

파이프라인 레지스터에 저장되기 전에는 명령어에 따라 유용한 값인지, 쓸모없는 값인지 판단할 수 없기 때문에 파이프라인 레지스터에는 모든 값이 모두 저장됩니다.

IF/ID (Instruction Fetch / Instruction Decode) Register

저장되는 값:

현재 클록 사이클에서 인출된 명령어 (Instruction)

다음 명령어를 가리키는 PC + 4 값 (프로그램 카운터 + 4): 분기 명령어 처리, 예외 발생 시 PC 복구 등에 사용될 수 있습니다.

역할: IF 단계에서 가져온 명령어와 다음 PC 값을 ID 단계로 전달하여 명령어 해독 및 레지스터 읽기에 사용되도록 합니다.

ID/EX (Instruction Decode / Execute) Register

저장되는 값:

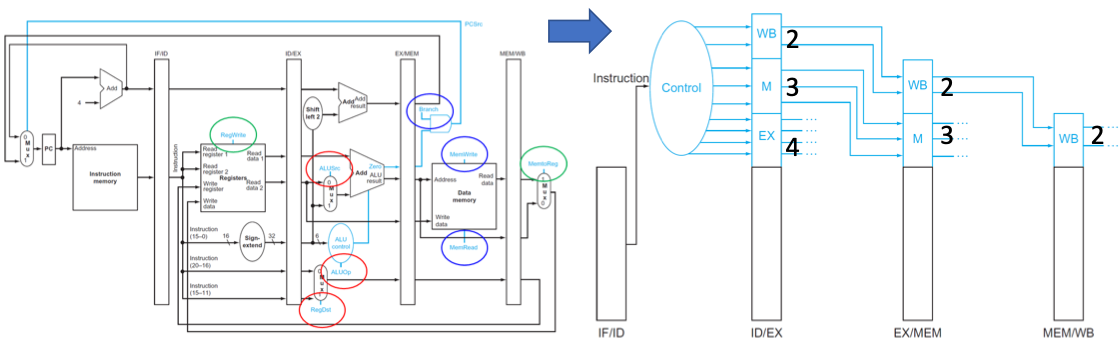

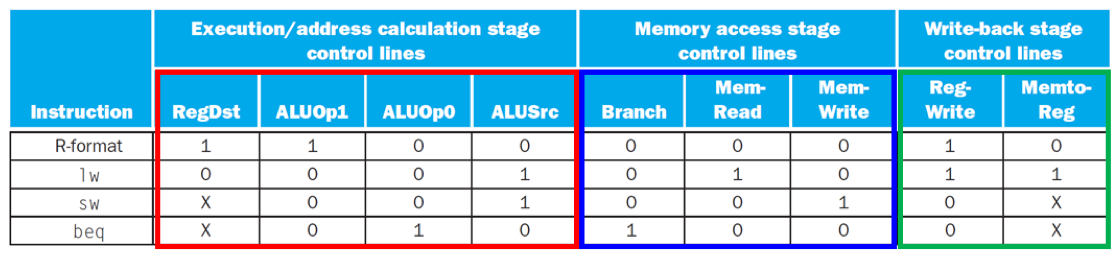

제어 신호 (Control Signals): EX, MEM, WB 단계에서 필요한 모든 제어 신호들 (예: RegWrite, MemRead, MemWrite, ALUSrc, ALUOp 등)이 이 단계에서 확정되어 이후 단계로 전달됩니다.

레지스터 파일에서 읽어온 두 개의 소스 피연산자 값 (Read Data 1, Read Data 2): 명령어의 rs, rt 필드에 해당하는 레지스터 값입니다.

부호 확장된 즉시 값 (Sign-extended Immediate Value): I-type 명령어(예: lw, sw, addi)에서 사용되는 즉시 값입니다.

PC + 4 값: 다음 명령어의 주소로, 분기 주소 계산이나 예외 처리 시 사용될 수 있습니다.

쓰기 레지스터 번호 (Destination Register Number): R-type 명령어의 rd 필드 값과 I-type 명령어의 rt 필드 값 (목적지 레지스터 번호). 이는 WB 단계에서 어떤 레지스터에 결과를 쓸지 결정하는 데 사용됩니다.

역할: ID 단계에서 해독된 명령어 정보와 레지스터 값을 EX 단계로 전달하여 연산 실행 및 주소 계산에 사용되도록 합니다.

EX/MEM (Execute / Memory Access) Register

저장되는 값:

제어 신호 (Control Signals): MEM, WB 단계에서 필요한 제어 신호들 (예: MemRead, MemWrite, MemtoReg, RegWrite 등)이 전달됩니다.

ALU 결과 (ALU Result): 연산 명령어의 결과값, 또는 메모리 접근 명령어의 유효 주소입니다.

레지스터 파일에서 읽어온 두 번째 소스 피연산자 값 (Read Data 2): store 명령어의 경우 메모리에 쓸 데이터 값으로 사용됩니다.

쓰기 레지스터 번호 (Destination Register Number): WB 단계에서 결과를 쓸 레지스터 번호입니다.

Zero 플래그 (Zero Flag): 분기 명령어에서 ALU 연산 결과가 0인지 여부를 나타내며, 조건부 분기에 사용됩니다.

분기 대상 주소 (Branch Target Address): 분기 명령어인 경우 점프할 주소입니다.

역할: EX 단계의 연산 결과와 메모리 접근에 필요한 정보를 MEM 단계로 전달하여 메모리 읽기/쓰기 작업에 사용되도록 합니다.

MEM/WB (Memory Access / Write Back) Register

저장되는 값:

제어 신호 (Control Signals): WB 단계에서 필요한 제어 신호들 (예: MemtoReg, RegWrite 등)이 전달됩니다.

ALU 결과 (ALU Result): 연산 명령어의 최종 결과 또는 load 명령어에서 읽어온 메모리 데이터의 주소입니다.

메모리에서 읽어온 데이터 (Read Data from Memory): load 명령어의 경우 메모리에서 읽은 실제 데이터 값입니다.

쓰기 레지스터 번호 (Destination Register Number): WB 단계에서 최종 결과를 쓸 레지스터 번호입니다.

역할: MEM 단계의 메모리 접근 결과(또는 EX 단계의 ALU 결과)를 WB 단계로 전달하여 최종적으로 레지스터 파일에 쓰여지도록 합니다.

Control Signal 전달

이러한 파이프라인 레지스터들은 각 단계가 다음 클럭 사이클에 필요한 모든 정보를 저장하고 전달함으로써, 파이프라인이 중단 없이 연속적으로 동작할 수 있게 해줍니다. 이는 데이터 해저드(data hazard)나 제어 해저드(control hazard)와 같은 문제를 해결하는 데 중요한 역할을 합니다.

키워드만 입력하면 나만의 학습 노트가 완성돼요.

책이나 강의 없이, AI로 위키 노트를 바로 만들어서 읽으세요.

콘텐츠를 만들 때도 사용해 보세요. AI가 리서치, 정리, 이미지까지 초안을 바로 만들어 드려요.